# A Survey of Co-Design Ideas and Methodologies $$(\mathrm{draft})$$

G. Bosman

$July\ 21,\ 2003$

# Contents

| 1        | Intr         | oduction                              | 1      |  |  |  |  |  |  |

|----------|--------------|---------------------------------------|--------|--|--|--|--|--|--|

|          | 1.1          | Traditional design                    | 1      |  |  |  |  |  |  |

|          |              | 1.1.1 Microprocessors                 | 1      |  |  |  |  |  |  |

|          |              | 1.1.2 Von Neumann bottleneck          | 2      |  |  |  |  |  |  |

|          |              | 1.1.3 Paradigm shift                  | 2      |  |  |  |  |  |  |

|          | 1.2          |                                       | 2      |  |  |  |  |  |  |

|          |              |                                       | 2      |  |  |  |  |  |  |

|          |              | 1.2.2 Programmable logic devices      | 3      |  |  |  |  |  |  |

|          |              |                                       | 3      |  |  |  |  |  |  |

|          | 1.3          | Assignment                            | 3      |  |  |  |  |  |  |

|          | 1.4          |                                       | 3      |  |  |  |  |  |  |

| <b>2</b> | Bac          | kground on Co-Design                  | 5      |  |  |  |  |  |  |

| -        | 2.1          |                                       | 5      |  |  |  |  |  |  |

|          | 2.2          | e e e e e e e e e e e e e e e e e e e | 5      |  |  |  |  |  |  |

|          | 2.3          |                                       | 5      |  |  |  |  |  |  |

|          | 2.0          | * *                                   | 5      |  |  |  |  |  |  |

|          |              | 1                                     | 6      |  |  |  |  |  |  |

|          |              |                                       | 6      |  |  |  |  |  |  |

|          |              | 1 0                                   | 6      |  |  |  |  |  |  |

| 3        | Co-          | Design                                | 7      |  |  |  |  |  |  |

| J        | 3.1          | 2 02.6                                | •<br>7 |  |  |  |  |  |  |

|          | $3.1 \\ 3.2$ | Modelling approaches                  |        |  |  |  |  |  |  |

|          | 0.2          | O Tr                                  | 9      |  |  |  |  |  |  |

|          |              | 0 0 0                                 | 9      |  |  |  |  |  |  |

|          | 3.3          | Validation                            | -      |  |  |  |  |  |  |

|          | 3.4          | Implementation                        |        |  |  |  |  |  |  |

|          | 5.4          | 3.4.1 Hardware/software partitioning  |        |  |  |  |  |  |  |

|          |              | 3.4.2 Synthesis                       |        |  |  |  |  |  |  |

|          |              | 3.4.3 Conclusion                      | _      |  |  |  |  |  |  |

| 4        | C            |                                       |        |  |  |  |  |  |  |

| 4        |              | aputational Models 13                 | _      |  |  |  |  |  |  |

|          | 4.1          | Properties of computational models    | -      |  |  |  |  |  |  |

|          |              | 4.1.1 Modelling of time               |        |  |  |  |  |  |  |

|          |              | 4.1.2 Orientation                     |        |  |  |  |  |  |  |

|          | 4.0          | 4.1.3 Main application                |        |  |  |  |  |  |  |

|          | 4.2          | Example: internal combustion engine   | 1      |  |  |  |  |  |  |

ii CONTENTS

|              | 4.3   | Common computational models             | 15        |

|--------------|-------|-----------------------------------------|-----------|

|              |       | 4.3.1 Continuous Time                   | 15        |

|              |       | 4.3.2 Discrete Time                     | 17        |

|              |       | 4.3.3 Discrete-Event                    | 17        |

|              |       | 4.3.4 (Co-Design) Finite-State Machines | 17        |

|              |       | 4.3.5 Kahn Process Networks             | 19        |

|              |       | 4.3.6 Asynchronous Data Flow            | 19        |

|              |       | 4.3.7 Synchronous Data Flow             | 19        |

|              |       | 4.3.8 Petri Nets                        | 19        |

|              |       | 4.3.9 Rendez-vous                       | 20        |

|              |       | 4.3.10 Synchronous/Reactive             | 20        |

|              |       |                                         |           |

|              | 4.4   | 4.3.11 Other Models of Computation      | 20        |

|              | 4.4   | Comparison                              | 21        |

| 5            | Rec   | uirements for Co-Design methodologies   | 23        |

|              | 5.1   | Paradigm shift                          | 23        |

|              | 5.2   | Origin of IDR                           | 24        |

|              | 5.3   | Design-space exploration                | 24        |

|              | 5.4   | Target architecture                     | 25        |

|              | 5.5   | Dealing with complexity                 | 26        |

|              | 0.0   | 5.5.1 Abstraction                       | 26        |

|              |       |                                         | 27        |

|              |       | 5.5.2 Hierarchy                         | 28        |

|              | T C   | <del>-</del>                            | _         |

|              | 5.6   | Conclusion                              | 28        |

| 6            | Co-   | Design methodologies                    | <b>29</b> |

|              | 6.1   | Ptolemy II                              | 29        |

|              | 6.2   | COSYMA                                  | 30        |

|              | 6.3   | ForSyDe                                 | 31        |

|              | 6.4   | Polis                                   | 31        |

|              | 6.5   | SpecC                                   | 32        |

|              | 6.6   | SystemC                                 | 32        |

|              | 0.0   | 6.6.1 SpecC vs. SystemC                 | 33        |

|              | 6.7   | VULCAN                                  | 33        |

|              | 6.8   | Comparison                              | 33        |

|              | 0.0   | Companion                               | 00        |

| 7            | Con   | aclusions                               | <b>37</b> |

|              | 7.1   | Internal design representation          | 37        |

|              | 7.2   | Co-Design approaches                    | 37        |

|              | 7.3   | Roadmap                                 | 38        |

| Bi           | blios | graphy                                  | 38        |

|              |       |                                         |           |

| $\mathbf{A}$ | Voc   | abulary                                 | 45        |

# Chapter 1

# Introduction

Designing embedded systems becomes more and more complex due to the increasing size of integrated circuits, increasing software complexity and decreasing time-to-market requirements and product costs. This ongoing increasing complexity of embedded systems motivates the search for a high-level system design approach at Chess. High-level system design is currently a major academic research area world-wide and it is strongly rooted in traditional areas such as control theory and digital design theory. For Chess such a design approach could mean a faster and better design process. This paper investigates aspects of high-level system design and the current state of the art in existing tools and methods that allow high-level system design. It will provide input for the Chess design strategy for the following years.

A system design notation should allow reasoning at a high level of abstraction. However, to be useful it must also be possible to synthesis hardware and software. Questions like how to divide the functionality of the system into hardware and software are a very important aspect of this synthesis. Traditionally the choice what to implement in hardware and what to implement in software is made early in the design process. Both parts are then made in separate tracks by separate design teams. Too often, the validity of this decision is not validated before system integration. This is far too late with respect to project risk.

When the emphasis lies on the hardware-software partitioning problem, system-level design methods are also called "Co-Design" methods. These terms are often used mixed; in this paper *Co-Design* will be mainly used.

The goal of Co-Design is to explore the whole design-space to be able to make well-informed critical design decisions. This would lead to a more optimal partitioning and more flexibility in the process from design to implementation. To really understand the improvement a high-level system design paradigm makes it is important to see how traditional system design works and what that approach lacks.

## 1.1 Traditional design

#### 1.1.1 Microprocessors

Traditionally complex embedded systems are designed around a microprocessor in a Von Neumann architecture. A Von Neumann system is fundamentally a

sequential system. There is heavy optimalisation inside the CPU itself (for instance using pipelining) but ultimately the commands are executed one at a time. Systems based on microprocessors have several benefits. Microprocessors are very well optimized and they allow design of families of products that can be built. Such a family of products can provide various feature sets at a different price point and can be extended to keep up with rapidly changing markets[50].

#### 1.1.2 Von Neumann bottleneck

However, the fact that each command is executed sequentially leads to a fundamental limitation. Backus calls this the "Von Neumann bottleneck" [2]. He points out that this bottleneck is not only a physical limitation, but has also been an "intellectual bottleneck" in limiting the way we think about computation and how to program.

## 1.1.3 Paradigm shift

This same aspect is a major motivation for Chess to do this investigation: how to prevent the 'paradigm-shift' that often occurs in designing systems. Some parts of an embedded system are easiest to describe using modelling languages that do not fit nicely onto existing hardware. Typical examples are data-filtering or physical movement modelling. A filter can be easily described in a drawing, and ultimately it is possible to imagine a specialized chip that implements this drawing immediately in gates. However, more commonly the algorithm will first be translated into C code, which will then be compiled into something to run on a CPU. The fundamental difference between these two approaches is their dealing with concurrency: if the drawing is implemented onto hardware directly, concurrent processing comes naturally. A translation to C code looses this advantage.

## 1.2 Other types of hardware

## 1.2.1 Application specific integrated circuits

Not all embedded systems are designed around microprocessors. It is possible to design embedded chips that compute in a parallel way. Application Specific Integrated Circuits (ASICs) are specialized chips that are used for example to implement encryption algorithms. They are similar to processors in the sense that they are also 'hardwired' solutions. It is very expensive to design an ASIC, and the design is a time-consuming process. Therefore, customizing an ASIC for a single application is only feasible when the project is reasonably large. In any case an ASIC can only be produced when the layout is final: it is not possible to experiment with the layout and try several versions.

Although you'll loose the optimalizations found in microprocessors there is a huge potential gain when designing hardware that is parallel in nature because the layout of the hardware can then be tailored exactly to the functional requirements. This can be extremely profitable, especially when the problem to be solved is mainly parallel in character. ASICs are therefore often used in areas such as compression or encryption which are parallel 'in nature'.

An important motivation for the rising interest in Co-Design is the introduction of another type of chip that is much more flexible than ASICs: programmable logic devices.

## 1.2.2 Programmable logic devices

Programmable Logic Devices (PLDs) are computer chips that can be programmed to implement circuits requiring both combinational and sequential logic. Reconfigurable logic devices are a class of programmable logic devices that may be reprogrammed as often as desired. A type of reconfigurable logic devices that are becoming very popular[10] are Field Programmable Gate Arrays (FPGAs). Three direct benefits of the reconfigurable approach can be recognized: specialization, reconfigurability and parallelism[43] [Guus: use more of Tessier on future developments [43]].

## 1.2.3 New design strategy

FPGA's shorten the development cycle dramatically and are much cheaper to use than ASICs. Their capacity has grown to a such a size that they can handle real application for a fair price for prototype series. This allows research in Co-Design to increase a lot and make it more worthwhile.

Early approaches in Co-Design started with components of high granularity, such as ASICs and microprocessors. Today parts of the hardware are designed from scratch on a FPGA in combination with microprocessor and ASICs. This allows the system to benefit from both the microprocessor's specialization and the parallelism offered by the FPGA and ASICs. A reason to (still) use ASICs and not to implement all the functionality in microprocessors and FGPAs is the power-consumption. The flexibility of the FPGA comes with the price that they are in general power inefficent compared to dedicated custom hardware [41]. Difference in granularity is an important feature to discriminate on various Co-Design approaches.

Obviously designing hardware and software for a system in an integral manner is an extremely complex task with many aspects. There is a wide range of architectures and design methods, so the hardware/software Co-Design problem is treated in many different ways.

## 1.3 Assignment

"To survey development methods and to investigate how an integrated approach of hardware-software design can improve system development at Chess."

The focus in this paper will be on the shift of paradigms when traversing through the various levels of detail.

## 1.4 Outline of this thesis

Chapter ?? gives an overview of related work. In Chapter 3 we'll look into the field of Co-Design and the problems it tries to solve. Different types of Co-Design approaches are described, and the classifications that can be made. It turns out that understanding the paradigms, the computational models, is very

important to decide on selecting a design strategy to use. Therefore Chapter 4 describes computational models that are commonly used to model (parts of) systems.

A single paradigm approach has serious disadvantages so various modelling approaches that allows a mixture of 2 or more computational models have been proposed in literature. To help investigating such approaches the various aspects of system-level modelling will be discussed in in Chapter 5. This Chapter will serve as a guide for Chess in assessment of future developments. In Chapter 6 a number of existing projects and models will be described and analyzed using the classifications and ideas found in the first part. This thesis ends with conclusions on the type of approaches there are, and which of these can be valuable for Chess.

# Chapter 2

# Background on Co-Design

This chapter describes the field of Co-Design.

## 2.1 Co-Design research

The field of Co-Design is about 10 years old now. Two papers that give a broad overview of the field are those by Gajski [15] and De Michelli[31].

## 2.2 Related work

- The SAVE project of the Linköping University in Sweden did a survey on Co-Design representation models in 1999[8].

- At the Leiden University in the Netherlands a survey was done comparing 8 tools and their underlying methodologies[49].

- O'Nils presented ComSys, an approach to the generation of interfaces between application software and hardware IP components. In his PhD thesis from 1999 he reviewed several Co-Design methods[35].

- Some authors made an broad overview of various Co-Design development methods, e.g. [51], [18].

- Edward Lee wrote a very readable introduction to the field of Embedded Software and various computational models[25] and how it is different from traditional computer science areas.

## 2.3 Related approaches

A number of areas that are related to Co-Design have been researched.

## 2.3.1 Software in the loop

Some of the issues Co-Design tries to solve are also handled by 'Software-In-The-Loop'. This is developing software in a virtual hardware environment. Although

this easies the design of software for hardware it does not allow the full improvements made possible by Co-Design because the partitioning between hardware and software is not flexible. Within Chess the SHAM has been developed. This is a device (a printed circuit board) that allows software testing for onboard software [45].

## 2.3.2 Reconfigurable hardware

Reconfigurable systems exploit FPGA technology, so that they can be personalized after manufacturing to fit a specific application.

"A promise of reconfigurable hardware is that it should allow the logic and memory resources in a chip to be used more efficiently, especially in applications that need massive computing power. But there is a further commercial advantage. It could turn finished products into a source of service revenue. Imagine a music player that includes programmable logic. When a new music-compression format emerges to replace MP3, owners of the player could download, for a fee, a new decompression algorithm for their player from the maker's website" [44].

Within Chess this opportunities have been recognized, and reconfigurable FPGA's are used in projects like ITA. This is a payment terminal, that can remotely get upgraded by downloading new software.

The operation of reconfigurable systems can either involve a configuration phase followed by an execution phase or have concurrent (partial) configuration and execution.[31]. The major problem in this type of systems consists of identifying the critical segments of the software programs and compiling them efficiently to run on the programmable hardware. This is a different field and will not be treated in this thesis.

## 2.3.3 Adaptive computing

The field of adaptive computation is closely related to reconfigurable hardware. According to Neema the primary challenge of the Adaptive Computing approach is in system design[33].

#### 2.3.4 Hybrid systems

Most traditional Co-Design methods explore ways of modelling digital systems. Embedded systems however, often interact with an analog environment. Traditionally, this is the domain of control theory and defined in the digital domain. Because of the way models are often treated (digital) the analog environment is often translated to a digital representation by computer scientists. This translation is not trivial but must be done very carefully otherwise it's not possible to formally verify guarantee safety and/or performance of the embedded device.

To address this issue *hybrid* embedded system models have been designed[1, 42]. The issues that Co-Design faces, such as combining various models of computations and making sure properties are valid throughout the whole design phase, can of course also be found in this hybrid system modelling.

# Chapter 3

# Co-Design

Co-Design is "A design methodology supporting the concurrent development of hardware and software in order to achieve system functionality and performance goals. In particular, Co-Design often refers to design activities prior to the partitioning into Hardware and Software and the activity of design partitioning itself." [47]

The Co-Design process for embedded systems includes specification, modelling, validation, and implementation[31]. To comprehend the benefits of various Co-Design technologies it is important to understand how the design process works. This process is the subject of this chapter.

## 3.1 Specification and modelling

Modelling is the process of conceptualizing and refining the specification. A specification undergoes a manual synthesis process that generates a model of an implementation. The result of the modelling phase is a model, which is specified in an Internal Design Representation (IDR)[18].

That model may contain multiple models of computation and there is a trade-off between scalability and expressiveness in this IDR[46].

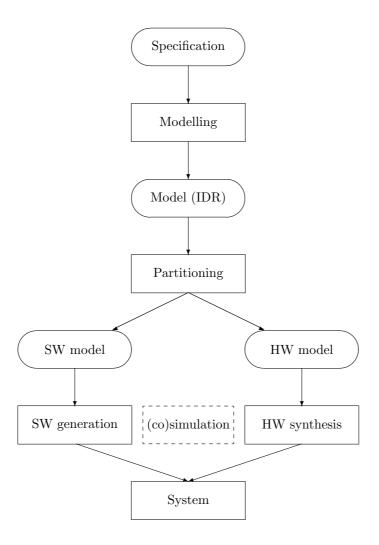

Modelling in the context of Co-Design is sometimes called *cospecification*. In Figure 3.1 the design process has been depicted, which will be described in this Chapter.

## 3.2 Modelling approaches

Hardware/software Co-Design of embedded systems can be differentiated in several ways. This thesis will distinguish approaches in the difference between the internal design representation. If there is a single IDR that is used throughout the development process, we'll call it a homogeneous modelling. Otherwise, when multiple IDRs are we'll call the approach heterogeneous.

Another possibility is to consider the number of system-level specification language. Mooney et. al. make this distinction: if a method has only a single specification language they'll call it a homogeneous approach, otherwise a heterogeneous approach [32]. I believe this is a bit to superficial, as very often

Figure 3.1: Co-Design design process

multiple specification languages can be used in the beginning of the specification process that are then mapped in one Internal Design Representation.

## 3.2.1 Modelling using a single IDR

Co-design starts with a global specification given in either a single language or in multiple languages that are converted into one IDR. This IDR should be independent of the future implementation and of the partitioning of the system into hardware and software parts. In this case Co-Design includes a partitioning step aimed to split this model into hardware and software. The outcome is an architecture made of hardware processors and software processors. This is generally called a virtual prototype and may be given in a single language or different languages[18].

This approaches is called compositional by Mooney, Coste[9]. It aims at integrating the partial specification of sub-systems into a unified representation which is used for the verification and design of the global behavior.

Many researchers are doubting whether a grand unified approach will work. Specifically the group of Edward A. Lee (who created the Ptolemy system) has doubt about this[6]. He calls modelling using a single IDR the 'grand unified method' [24]. In order to be sufficiently rich to encompass the varied computational models of the competing approaches. They become unwieldy, too complex for formal analysis and high quality synthesis. Lee sees it as a big problem that a homogenous approach is based on a single IDR. This IDR would impose a model of computation which might be good for a subset of systems but bad for others[24].

Examples of homogeneous methods are Polis, COSYMA and SpecC.

## 3.2.2 Modelling using multiple IDRs

Lee states that generality can be achieved through heterogeneity, where explicit more than one model of computation is used. Coste calls this the co-simulation based approach[9].

Heterogenous modelling allows the use of separate languages for the hardware and software parts. The Co-Design starts with a virtual prototype where the hardware/software partitioning is already made for the biggest part. This a fundamental difference with the homogeneous approach. Here the emphasis is on the integral designing of the parts to make sure that the overall system has the required properties. The key issues are validation and interfacing [18]. A lot of research is done on the integration of different system parts that enables system optimization across language boundaries.

The co-simulation-based approach consists in interconnecting the design environments associated to each of the partial specifications. Like its name suggests, with co-simulation the software processors and the hardware processors of an system and their interactions are simulated in one simulation. It does not provide such a deep integration as compositioning does [stelling, leg uit]. However it does allow for modular design. Communication is between the processors would typically be implemented using a cosimulation bus which is in charge of transferring data between the different simulators.

Sometimes cosimulation is used to simulate the behavior of a system consisting of 2 models: the hardware and the software, and sometime it is used to

model on a more abstract level where the hardware vs software decision has not been made yet. [Hmm. Strijdig met hierboven!] A typical example of such a co-simulation approach is Ptolemy II.

## 3.3 Validation

The validation process a design model should give the designer a reasonable level of confidence about how much of the original embedded system design will be in fact be reflected in the final implementation [46]. There has been a lot of research in the simulation of heterogeneous hardware/software systems [6, 23, 46]. There are 3 three methods for validation:

- 1. Simulation

- 2. Prototyping

- 3. Formal Verification

Most design methods incorporate validation throughout the whole design process. Early in the design process simulation is mostly used. Some design methods support this explicitly. For example, some models are so detailed that they allow 'execution', on a very high level. More often, simulation is used after the partition step but before the hard- and software synthesis. In that context the term 'co-simulation' is often used.

Formal verification allows for a more thorough evaluation of the embedded system behavior (maximum behavioral coverage) by means of logics.

It is good to note that in simulation the hardware is often simulated (although often not real-time, as it's just a simulation). However there has also been some research in replacing the hardware simulator with an FPGA that simulate the real target hardware[23].

## 3.4 Implementation

The model found throughout the modelling phase has to be implemented into hardware and software. It is an important notion in a Co-Design approach that there must be no continuity problem. That is: the steps from model to the synthesis should be all in the design process[40].

In the implementation phase architectural information is taken into account. Varea[46] calls this a merger between the IDR and the *technology library*. It is important that the intermediate IDR or specification is not too much influenced by the current target technology. Steps in the implementation phase include:

- 1. Hardware/Software partitioning

- 2. Synthesis of the code for software and hardware

## 3.4.1 Hardware/software partitioning

'In the case of embedded systems, a hardware/software partition represents a physical partition of system functionality into application-specific hardware and

software executing on one (or more) processor(s)'[31]. Partitioning is the a crucial step in Co-Design. The model must be split into parts: parts software, parts hardware. The most ideal would be to have *automatic partitioning*, in which tools will take the model and the target architecture into account, and make the split automatically. For this, it is important that the target architecture is known by the tools. In Chapter 5.3 there will be more about that.

The partitioning step is deliberately left vague here, as it differs strongly per design method. Often the partitioning step will be split into sub-steps, each dealing with a specific part of creating the split, such as scheduling and interface synthesis (see for example [15]. Other design methodologies don't have a single partitioning step. Instead before the final code and hardware synthesis, there is an iterative process of refining and transformation, such as in ForSyDe[39].

## 3.4.2 Synthesis

On the lowest level, FPGA's can be used to implement SM's, datapaths and nearly any digital circuit. The outcome of the synthesis process is a final implementation of the embedded system. As an extra validation step the result of the implementation is often checked by creating a small amount of prototypes first.

#### 3.4.3 Conclusion

The discussion of homogeneous vs. heterogeneous modelling and about IDRs is related to the fact that a particular IDR has an area of application to which it fits best.

The following chapter gives a rationale about this phenomena.

# Chapter 4

# Computational Models

Modelling is at the heart of all development methods. All Co-Design systems are based on a computational model, or combine a few of them. The computational models can be found in the Internal Representation Language. In this Chapter common computational models are described and compared. In Chapter 4.2 a running example is introduced.

A computational model is a formal, abstract definition of a computer. It describes the components in a system and how they communicate and execute [28].

## 4.1 Properties of computational models

There are three characteric properties of computational models important for system design:

- 1. Modelling of time

- 2. Orientation

- 3. Main application

## 4.1.1 Modelling of time

An essential difference between concurrent models of computation is their modelling of time. [24] (page 11). Lui[27] states that the different notions of time make programming of embedded systems significantly different from programming in desktop, enterprize or Internet applications. Lee[26] proposed a mathematical framework to compare certain properties of models of computation. This allows for a precise definition of the various computational models. Time modelling alternatives are:

- continuous time, real numbers are taken as time-axes (see 4.3.1)

- discrete time, there's a global clocktick

- partial ordered time, events are ordered

- No explicit notion of time

A very useful trick in dealing with time is assuming synchrenous operations. The synchrony hypothesis forms the base for the family of synchronous languages. It assumes, that the outputs of a systems are synchronized with the system inputs, while the reaction of the system takes no observable time. So time is abstracted away. The synchrony hypothesis abstracts from physical time and serves as a base of a mathematical formalism.

'In synchronous languages, every signal is conceptually (or explicitly) accompanied by a clock signal. The clock signal has meaning relative to other clock signals. It defines the global ordering or events. Thus, when comparing two signals, the associated clock signals indicate which events are simultaneous and which precede or follow others. A clock calculus allows a compiler to reason about these ordering relationships and to detect inconsistencies in the definition.'[6].

Whether or not a language is synchronous has quite big implications. It is therefore also added in the matrix add the end of this Chapter.

#### 4.1.2 Orientation

Gajski distinguises five categories of models[15]:

- State-oriented

- Activity-oriented

- Structural-oriented

- Data-oriented

- Heterogeneous

Additionaly 'timed' models of computation can be recognized.

#### 4.1.3 Main application

Fundamental to embedded software is the notion of concurrency. There is a lot of research done on compiling concurrent languages into sequential code that can be run on a microprocessor, see for example [19]. For this thesis however it is more interesting to see what happens when this paradigm-shift does not have to be made.

There are models that are designed to describe dataflow oriented systems (ie DSPs) and there are models more suitable for control-flow systems. However this approach lacks generality as most systems are not easily put in either one category. It should be noted that the difference between a control-flow or data-flow oriented computational model is important for both control and data-oriented systems. Many control-systems use complex sensors or subsystems such as image processing algorithms that are best specified using a type of data-oriented computational model [28].

## 4.2 Example: internal combustion engine

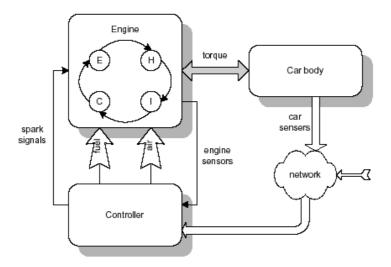

A good illustration of the need for multiple computational models can be found in [27], where the working of an internal combustion engine is described using various models of computation:

Figure 4.1: An internal combustion engine is made up of several parts that should be modelled by different MoCs. Adopted from Liu[27].

A cylinder of an internal combustion engine has four working phases: intake, compress, explode, and exhaust. The engine generates torque that drives the power train and the car body. Depending on the car body dynamics, the fuel and air supply, and the spark signal timing, the engine works at different speeds, and thus makes phase transitions at various time transitions. The job of the engine controller is to control the fuel and air supplies as well as the spark signal timing, corresponding to the drivers demand and available sensor information from the engine and the car body.

The engine and the car body in this example are mechanical systems, which are naturally modelled using differential equations. The four phases of the engine can be modelled as a finite state machine, with a more detailed continuous dynamics for the engine in each of the phases. While all the mechanical parts interact in a continuous-time style, the embedded controller – which may be implemented by some hardware and software – works discretely.

Additionally, sensor information and driver's demands may arrive through some kind of network. The controller receives this information, computers the control law, controls the air and fuel values, and produces spark signals, discretely. So, we want to use a model that is suitable for handling discrete events for the network and the controller.

In this very common example, we have seen both continuous-time models and several discrete models: finite state-machines, discrete events, and real-time scheduling. These models, and other, will be described in the rest of this Chapter.

## 4.3 Common computational models

#### 4.3.1 Continuous Time

As we saw above a computational model describes components and their interac-

| Time         | Continuous, |

|--------------|-------------|

|              | global      |

| Orientation  | Timed       |

| Synchronous? | -           |

| Main app.    | Mechanical  |

|              | parts,      |

|              | analog      |

|              | circuits    |

tions. Embedded systems often contain components that can best be described using differential equations. Differential equations describe the rate at which variables change. They are often used to model (electro-)mechanical dynamics, analog circuits, chemical processes and many other physical systems[13].

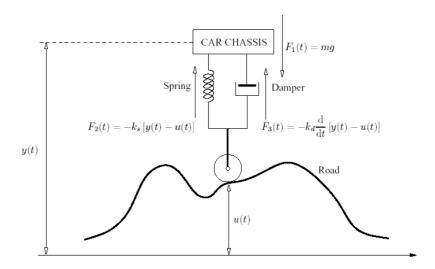

Figure 4.2: Forces on a car shock absorber that result in a differential equation relationship between road height signal u(t) and the car height signal y(t) [34].

In our car controller example of Chapter 4.2 the mechanical behavior of the engine and the car body are good candidates of components that can well be described using differential equations. Mechanical systems are often described using large number of difference equations, that can be hard to understand. In [34] a relatively easy example is given. It shows how mechanical interactions quickly lead to differential equations (thus to a continuous model).

In Picture 4.3.1 the chassis of a car is depicted and how it's connected to the road with a spring and damper. The interaction of these 3 physical forces (gravity, the spring and the damper) lead to a differential equation (Equation 4.1).

$$\frac{d^2}{dt^2}y(t) + \frac{k_d}{m}\frac{d}{dt}y(t) + \frac{k_s}{m}y(t) = g + \frac{k_d}{m}\frac{d}{dt}u(t) + \frac{k_s}{m}u(t)$$

(4.1)

This differential equation gives a relationship between the road-height and the car-height. For an embedded car-control system this can be important information; for example to slow down the car when the shocks are getting bigger.

Fundamental to this computational model is that it uses real numbers as time model – that's why this model is called continuous time. Formally said: "continuous-time systems are active over the entire time axis processing their input and producing output" [42]. The 'execution' of a continuous time model mean that a so-called *fixed point* must be found by the execution environment.

This means that a set of functions of time must be found that satisfy all the relations. Hybrid systems (see Chapter 2.3.4) specifically deal with the integration of these type of Computational Models with others.

#### 4.3.2 Discrete Time

Difference Equations are a discrete counterpart of differential equations. Where the latter works in the continuous time difference equations are discrete time based. Discrete-time systems can only react to their input and produce new output at distinct, equidistant time instances [42]. Difference equations are often rearranged as a recursive formula so that a systems output can be computed from the input signal and past outputs. Difference equations are commonly used for modelling *filters* (that manipulate sound) and periodically sampled data streams. They can been seen as discretized version of differential equations.

| Time         | Discrete,    |

|--------------|--------------|

|              | global       |

| Orientation  | Timed        |

| Synchronous? | -            |

| Main app.    | Filters,     |

|              | periodically |

|              | sampled      |

|              | data         |

#### 4.3.3 Discrete-Event

In a discrete-event system, modules react to event that occurs at a given time instant and produce other events either at the same time instant or at some future time instant. Execution is chronological[6]; time is an integral part of the model. Events will typically carry a time stamp, which is an indicator of the time at which the event occurs within the model. A simulator for Discrete-Event models will typically maintain a global event queue that sorts events by time stamp. This sorting can be computationally costly. [Guus: hard to simulate, nice in hardware].

| Time         | Sorted       |

|--------------|--------------|

|              | events,      |

|              | global       |

| Orientation  | Timed        |

| Synchronous? | -            |

| Main app.    | Digital cir- |

|              | cuits        |

## 4.3.4 (Co-Design) Finite-State Machines

The finite-state machine model has been widely used in control theory and is the foundation for the development of several models for control-dominated embedded systems. The classical Finite State Machine (FSM) consists of a set of states, a set of inputs, a set of outputs, a function which defines the outputs in terms of input and states and a next-state function. [8].

FSMs model systems where the system at any given point in time can exist in one of finitely many unique states. This makes them excellent for control logic in embedded systems. They can very well be formally analyzed and it is relatively straightforward to synthesis code from this model [24].

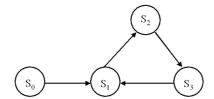

FSM can be visualized very well using a state transition graph (see Figure 4.3.4). FSM have a number of weaknesses. They are not very expressive, and the

| Time         | Events     |

|--------------|------------|

|              | with time- |

|              | stamp      |

| Orientation  | State      |

| Synchronous? | No         |

| Main app.    | Control-   |

|              | parts      |

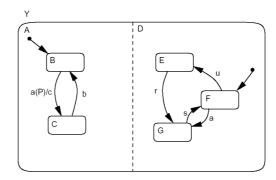

Figure 4.3: A state transition graph.

Figure 4.4: Hierarchical concurrent states[15].

number of states can get very large even in the face of only modest complexity. Is intended for control-oriented systems with relatively low algorithmic complexity.

#### Extensions of the FSM

A number of variations has been proposed to overcome to weaknesses of the classical FSM model. Using FSMs in a hierarchical model was first made popular by Harel[28]. He proposed StateCharts, which combine hierarchical FSMs and concurrency. Statecharts are essentially a combination of FSMs with a SR. The tools Statemate from Ilogix uses statecharts as its control specification model.

In cases when a FSM must represent integer or floating-point numbers, a state explosion problem could be encountered. If each possible value for a number requires a state, the FSM could require a enormous amount of states. This can be solved by introducing a data-path to the FSM. This solution was described by Gaiski[15]; it could be used for computation-dominated systems.

An obvious extension to the FSM would be the addition of concurrency and hierarchy. Such a system is then called a Hierarchical Concurrent FSM (HCFSM). Like the FSM, the HCFSM models consists of a set of states and transitions. However, each state of the HCFSM can be further decomposed into a set of substates, thus modelling hierarchy. Each state can also be decomposed into concurrent substates which execute in parallel and communicate through global variables. An example can be seen in picture 4.3.4. State Y is decomposed in two concurrent states, A and D. The bold dots in the figure show when the starting point of the states are.

Perhaps the most successful extension to the classical FSM is the Co-Design Finite State Machine (CSFM) which is used in Polis. In Chapter 6.4 we'll see more about this. Important in this extension is the hierarchy and concurrency that are added. The communication primitive in the CSFM system is the *event*. The behavior of the system is defined as sequences of events that can be observed when interact with the environment [8]. The notion of time in this model is thus: events with a time-stamp (ordered time).

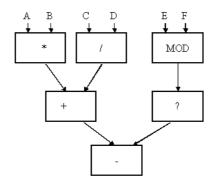

Figure 4.5: A dataflow graph for  $(a * b) + (c/d) - \sqrt{(e \mod f)}$ .

#### 4.3.5 Kahn Process Networks

In a process network model of computation the arcs represent sequences of data values (token) and the bubbles represent functions that map input sequences into output sequences. Certain technical restriction are necessary to ensure determinacy. [24].

| 4.3.6 | Asynchronous | Data | Flow |

|-------|--------------|------|------|

|       |              |      |      |

It is a common representation formalism for modeling algorithms. The graph representation can be interpreted asynchronous (ADF) or synchronous (SDF). Special case of Kahn process networks.

## 4.3.7 Synchronous Data Flow

#### 4.3.8 Petri Nets

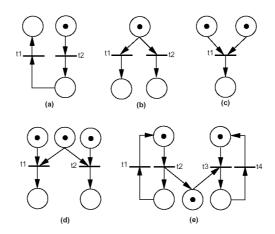

A Petri net is a well-known graphical and mathematical modeling tool. A Petri Net is a bipartite graph of transitions and places connected by directed edges. Each place has a number of tokens which are not ordered and at least in the basic Petri net model do not carry additional information.

In the classical approach a Petri net is composed of 4 basic elements: a set of places, a set of transition, an input function that maps transitions to places, and an output function which is also a mapping from transition to places.

A Petri net executes by mean of firing transitions. A transition can fire only if it is enabled – that is, if each of its input places has at least one token. Transitions may fire if each of its input places contains at least as many tokens as there are edges from the input place to the transition. At firing, a transition removes one token via each incoming edge and produces a token via each outgoing edge.

Two important features of Petri nets are its concurrency and asynchronous nature. [8], this can be modelled quite naturally as seen in Picture 4.3.8.

It can be considered both activity- and state-based model, depending on the exact interpretation used in the modelling approach.

| Time         | No explicit |

|--------------|-------------|

|              | timing      |

| Orientation  | Activity    |

| Synchronous? | No          |

| Main app.    | Digital     |

|              | signal      |

|              | processing  |

| Time         | No explicit |

|--------------|-------------|

|              | timing      |

| Orientation  | Activity    |

| Synchronous? | No          |

| Main app.    | Digital     |

|              | signal      |

|              | processing  |

| Time         | No explicit |

|--------------|-------------|

|              | timing      |

| Orientation  | Activity    |

| Synchronous? | Yes         |

| Main app.    | Digital     |

|              | signal      |

|              | processing  |

| Time         | Order of    |

|--------------|-------------|

|              | transitions |

| Orientation  | State or    |

|              | activity    |

| Synchronous? | No          |

| Main app.    | -           |

Figure 4.6: Petri net representing: (a) sequential order, (b) branching, (c) synchronization, (d) resource contention and (e) concurrency[15].

| Time         | Atomic    |

|--------------|-----------|

|              | events on |

|              | timeline  |

| Orientation  | State     |

| Synchronous? | No        |

| Main app.    | Modelling |

|              | resource  |

|              | manage-   |

|              | ment      |

## 4.3.9 Rendez-vous

In a rendezvous model, the arcs represent sequences of atomic exchanges of data between sequential processes, and the bubbles presents the processes. [24]. Examples are Hoare's CSP and Milner's CCS. This model of computation has been realized in a number of concurrent languages, like Lotos and Occam.

An example of a design tool for embedded (control) systems based on this computational model is the CTJ (Java) library developed by Jovanovic et. al.[20].

| Time         | No explicit  |

|--------------|--------------|

|              | timing       |

| Orientation  | Timed        |

| Synchronous? | Yes          |

| $Main\ app.$ | Reactive     |

|              | real- $time$ |

## 4.3.10 Synchronous/Reactive

In synchronous languages, modules simultaneously react to a set of input events and instantaneously produce output events. If cyclic dependencies are allowed, then execution involves finding a fixed point, or a consistent value for all events at a given time instant. [6]

Very often real-time systems are specified by means of concurrent processes, which communicate asynchronously [39].

## 4.3.11 Other Models of Computation

In this Chapter a number of computational models have been discussed. However, this list is not complete. There are many extension and variants of the computational models we've seen. Specifically Petri Nets are being researched a lot, such as Coloured Petri Nets and High Level Petri Nets. These can often be used well as Internal Design Representations. Varea proposed an IDR called Dual Flow Net (DFN), which provides tight control and data flow interaction[46]. Another mixed IDR is FunState, which are functions driven by state machines.

Another way that can be used to specify a model in a Co-Design method are imperative programming languages. The IDR would then be the syntax graph of the language. This has the disadvantage that programming are too complex to use in formal verification, and that (imperative) programming languages do not explicitly model the system's state. The latter makes them harder to use in modeling embedded systems. Technically, such an IDR is often an 'Control/Data-Flow Graph', but in this paper it will be refered to a 'Syntax Graph'.

## 4.4 Comparison

Table 4.1: The main characteristics of the models of computation described in this Chapter.

| Computational model        | Time               | Synchronous? | Orientation   | Main application   |

|----------------------------|--------------------|--------------|---------------|--------------------|

| Continuous Time            | Continuous,        | -            | Timed         | Continuous con-    |

|                            | global notion of   |              |               | trol laws, mechan- |

|                            | time.              |              |               | ical parts, analog |

|                            |                    |              |               | circuits           |

| Discrete Time              | Global notion of   | -            | Timed         | Periodically sam-  |

|                            | time. Every signal |              |               | pled data systems, |

|                            | has a value at ev- |              |               | cycle accurate     |

|                            | ery clock tick[28] |              |               | modelling          |

| Discrete-Event             | Globally sorted    | -            | Timed         | Digital circuits   |

|                            | events with time   |              |               |                    |

|                            | tag                |              |               |                    |

| (Co-Design) Finite         | Events with time-  | no           | State         | Control-parts      |

| State Machine <sup>a</sup> | stamp              |              |               |                    |

| Kahn Process Net-          | No explicit timing | no           | Activity      | Digital Signal     |

| works                      |                    |              |               | Processing         |

| SDF                        | No explicit timing | yes          | Activity      | Digital Signal     |

|                            |                    |              |               | Processing         |

| ADF                        | No explicit timing | no           | Activity      | Digital Signal     |

|                            |                    |              |               | Processing         |

| Petri Nets                 | No explicit tim-   | no           | State- or ac- | Scheduling, con-   |

|                            | ing. Just order of |              | tivity        | trol, network pro- |

|                            | transitions[8]     |              |               | tocols             |

| Rendez-vous                | Atomic events      | no           | State         | Modelling re-      |

|                            | along line of      |              |               | cource manage-     |

|                            | time[8]            |              |               | ment problems      |

| Synchronous/Reactive       | No explicit timing | yes          | Timed         | Reactive real-time |

<sup>&</sup>lt;sup>a</sup>The Codesign Finite State Machine is chosen as a representative because the basic FSM is not sophisticated enough to be used as a Model of Computation (see 4.3.4).

Three important characteristics have been described in Table 4.4. It shows

that there are a number of computational models suitable for digital signal processing (the dataflow and process networks). Others are suitable mainly for control-oriented work (CSFM, synchronous/reactive). This indicates that for a real system various MoCs are necessary. Experience also suggest that several MoCs are required for the design of a complete system[6].

Next to the computational models discussed in this Chapter, there is a lot of research into new Internal Design Representations, such as Dual Flow Nets and FunState. These are still experimental, and there are no methodologies using these IDRs.

The formal computational models are not the only way a model can be specified; some design methods use the syntax graph of an imperative programming language as their IDR.

Because of the very different notions of time in the various MoC's, ranging from continuous time to no time-notion at all, integrating them is by no means trivial. This is one of the problems Co-Design approaches must solve before they're usable in system-design. In the next chapter various problems will be analyzed.

# Chapter 5

# Requirements for Co-Design methodologies

In this chapter requirements for usable Co-Design methods are discussed. The result of this Chapter is a list of requirements and important aspects of Co-Design methodologies.

## 5.1 Paradigm shift

It has been recognized in literature that there is an important relationship between the model of computation and the target-architecture. Kienhuis et al. [22] speak in this context about a mapping between a model of computation and the architecture: "In mapping we say that a natural fit exist if the model of computation used to specify applications matches the model of architecture used to specify architectures and that the data types used in both models are similar." This concept of a natural fit is the same concept of preventing a paradigm shift; when there is a natural fit between the application's IDR and the target architecture then there is no paradigm shift. This concept is thus recognized by the research community. However, a question they are still facing is how to integrate these various models of computation. As we saw in Chapter 3 there are basically two approaches:

How is integration of computational models dealt

- Using a single IDR (compositional approach)

- Using more than one IDR (co-simulation approach)

The main difference in the two approaches in my view is that the co-simulation approach allows for more MoCs in a methodology and are better capable of working with optionally new developed MoCs. The other option promises a closer integration. This relates to the conventional wisdom that high performance while minimizing resources needed (or time needed) can be obtained by matching the architecture to the algorithm[33].

#### 5.2 Origin of IDR

Many languages and tools that were developed based on a single model start to embrace other models [13]. The downside of such large languages that compose multiple MoC's in an ad hoc fashion is that formal analysis may become very difficult[6]. It compromises the ability to generate efficient implementations or simulations and makes it more difficult to ensure that a design is correct. It precludes such formal verification techniques as reachability analysis, safety analysis and liveness analysis.

This is not to be said that compositional approach doesn't work. It does mean that a language should take the ability to integrate MoCs in it's design from the beginning. In this sense it's important to realize that it's not the language itself, but the IDR that a language will be converted in is fundamental. A lot of research goes into composite MoCs, suitable for both data- and controlflow. We saw for example some extensions of the classic FSM in Chapter 4.3.4. Varea[46] proposes a classification for internal design representations according to the following taxonomy:

- 1. Models originally developed for control-dominated embedded systems and later expanded to include data-flow (these models will be called  $\mathcal{M}_{CD}$ ).

- 2. Models developed in a data-dominated basis extended to support also control flow (referred to as  $\mathcal{M}_{DC}$ )

- 3. Unbiased model developed specifically to deal with combined control/data-

flow interactions  $(\mathcal{M}_{\overline{k}})$

Such a classification can be useful to discriminate between various approaches. As noticed in Chapter 2.3.4 the modelling of hybrid digital-analog systems is a related field that is gaining more attention too. Also in this field there are existing tools that are extended with functionality to deal with hybrid modelling. An example of this is VHDL-AMS[7], or another example is SimuLink, a framework that is commonly used [27]. It's a modelling and simulation environment for continuous-time dynamic systems with discrete events that recently has been extended with statemachine modelling of discrete control[1].

#### 5.3 Design-space exploration

Many parts in the design of embedded systems require manual decisions. Some Co-Design methods try to automate an important part of the design process: the decision what parts to implement in hardware, and what on software. This is called automatic partitioning.

However, this is certainly not easy for a design methodology. In fact, most of them don't support it. Still, even with methodologies that don't have automatic partitioning, Co-Design is valuable. It makes validation and synthesis of code a lot easier, because of the shared model (IDR) that has been made.

Because of the complexity of most systems, optimal manual decisions are sometimes not feasible. There are simply too many possibilities to consider. To use all of the potential improvements that a later HW/SW partition decision allows, it is therefore very important to reduce the user decisions as far as possible. This has been recognized and there are various methods for systematic design

What is the origin of the IDR of the approach?

Is automatic partitioning supported?

space exploration [5]. "In order to perform rigorous analysis and synthesis it is essential to prune the design space retaining only the most viable alternatives." In the past heuristics have been used to prune large design spaces. However, due to the complex behavior and interactions in multi-modal systems it is difficult to come up with effective heuristics. A better approach is to use constraints to explore and prune the design spaces; constraint satisfaction can eliminate the designs that do not meet the constraints. The pruned design space contains only the designs that are correct with respect to the applied constraints. These designs can then be simulated, synthesized and tested." [33].

Is there a possibility of design-space exploration in the approach?

#### 5.4 Target architecture

When a Co-Design methodology allows for the generation of both software and hardware, it must also generate the communication mechanisms between these two parts. This include the operating system perhaps, and the device drivers of some sort.

Not only the design process can be improved. Many suggestions brought up Does the approach allow IP in this Chapter deal with the methodology itself. However, O'Nils point out that very often off-the-shelf IP components are used in system design, and that often a major part of the work will be in interfacing these IP components. Tools like Polis are primarily designed for cases in which the whole design functionality is captured within the tools environment and communication refined during system synthesis. That is, the device drivers are generated together with the custom hardware and the operating system. However, if users want tot use IP blocks and off-the-shelf operating systems they will face the same problems that occur in manual design[35]. This has important implications for the commercial use of Co-Design methods and design space exploration tools: if they don't take into account off-the-shelf IP components they are not suitable for many types of projects. So next to the design methodology and design process itself, there is also the matter of whether or not IP reuse is explicitly supported.

Keutzer et al. state: "We actually believe that worrying about HW-SW boundaries without considering higher levels of abstraction is the wrong approach. HW/SW design and verification happens after some essential decisions have been already made, and this is what makes the verification and the synthesis problem hard. SW is really the form that a behavior is taking if it is "mapped" into a programmable microprocessor or DSP. [...] The origin of HW and SW is in behavior that the system must implement" [21].

It is possible to generate a complete system using only FPGA's, but it's more common to use a combination of 1 (or more) processors with dedicated hardware (ASIC's) or with flexible hardware (FPGAs). This is combination of processor with extra hardware is called *coprocessing*[31], and the term *co-processor* is often used for the ASIC's.

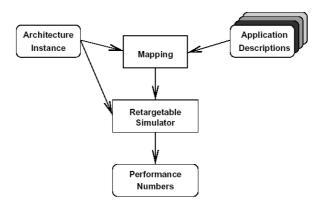

The issue here is thus to create a useful mapping between an application and a target architecture. There is a design-space exploration method that is build on this premise, the Y-Chart approach as proposed by Kienhuis [22]. This method follows a general scheme that can be visualized by an Y-shaped figure

What type of target architectures are supported?

<sup>&</sup>lt;sup>1</sup>This term is rather unfortunate, as there exists another Y-Chart in Co-Design. The Gajski Y-Chart was introduced in 1983 for describing the taxonomy of electronic systems in 3 dimensions: behavioral, structural and physical.

Figure 5.1: The Y-Chart approach[22].

(see Figure 5.4). In the upper right part in that Figure is the set of application descriptions that drives the design of the architecture. The effectiveness of the initial architecture is to be evaluated, using performance measurements. The various applications will be mapped on the architecture, and using quantitative numbers the performance will be determined. If this doesn't match the requirements, either the applications or architecture should be changed.

The power of this method is seen when these steps are supported by the development method. Therefore it is required to allow architecture to be defined within the same method, and to perform performance analysis. Newer Co-Design methods, such as Ptolemy II and SpecC have tools that help with design-space exploration.

## 5.5 Dealing with complexity

## 5.5.1 Abstraction

It is obvious that low-level languages such as VHDL are able to implement different models of computation. An imperative language can be used to implement for example a dataflow MoC[6].

However, lack of abstraction disqualifies low-level languages as candidates for modelling combined computational model-systems because it leaves programmers no freedom to make trade-offs between programmability, utilization of resources and silicon area. It's common for a specification language to allow more than 1 model of computation. However this does not always mean that this allows for suitable high-level mixture of 2 models.

A goal of all design methods is to allow systems to be designed on a higher level than the implementation level. The ultimate goal is to allow a very high-level design, that then automatically can be converted into the implementation level. This is a fundamental notion in computer science. Examples are programming languages, that allow humans to reason about variables or flow-of-control on a much higher level than machine code allows. There has also been a lot of re-

search into finding languages to design hardware from a higher level. Nowadays it is very common to use a language as VHDL to define hardware. There are compilers available to generate netlists (hardware descriptions) from languages like VHDL. Although VHDL is probably considered by software engineers to be low-level, it is a major step forward compared to the arcane art of programming cells and gates directly.

This looking for a higher level of abstraction is an ongoing quest, and as so it can also be found in Co-Design methods. Ultimately the goal is to be able to design a system in a textual or graphical way, in such a manner that there will be an automatic compiler from this high-level representation into the implementation level: hardware, software or (often) a combination of both. Sometimes such an approach is called model compilation [40].

A higher level of abstraction in modelling decreases the gap between functional requirements of a system and the modelling process, leading to a better fit between these. There is of course no definition for "high level" or "lower level". Still, we'll try to get a view of a method by looking at the level of its specification language(s), and stay in line with Jerraya[18], who also used these words. In our result we'll make a difference in 3 levels: low, medium and high-level specification language.

What is the abstraction level used in the methodology?

## 5.5.2 Hierarchy

'Brute-force composition of heterogeneous models may cause emergent behavior. Model behavior is emergent if it is caused by the interaction between characteristics of different formal models and was not intended by the model designer.'[13]

A common way to prevent unwanted emergent behavior is isolating various subcomponents and letting these subcomponents work together in a hierarchical way. Hierarchical in the sense of a containment relation, where an aggregation of components can be treated as a (composite) component at a higher level. In general, hierarchies help manage the complexity of a model by information hiding – to make the aggregation details invisible from the outside and thus a model can be more modularized and understandable[27]. We're talking about behavioral hierarchy here – composition of child behaviors in time, as opposed to structural hierarchy.

"Note that in Ptolemy, models of computations are mixed hierarchically. This means that two MoC's do no interacts as peers. Instead, a foreign MoC may appear inside a process. In the old version of Ptolemy, such a process is called a wormhole. It encapsulates a subsystem specified using one MoC within a system specified using another. The wormhole must obey the semantics of the outer MoC at its boundaries and the semantics of the inner MoC internally. Information hiding insulates the outer MoC from the inner one." [6]. This approached of worm-holes was a bit biased towards data-flow computational models. In Ptolemy II it was replaced with opaque composite actors[11]. [Guus: explain the difference between composite actors and worm-holes!]

There are other ways to mix models of computation too. Statemate uses views. [Guus: are these views related to what Jantsch[17] calls analytical slicing into domains?]

## 5.5.3 Implementation

A discrete-event model of computation is well suited for generating hardware. It is not very suitable to generate (sequential) software[6]. This is for example why VHDL simulation surprises the designer by taking so long. A model that heavily uses entities communicating through signals will burden the discrete-event scheduler and slow down the simulation. Thus, a specification built on discrete-event semantics is a poor match for implementation in software.

By contrast, VHDL that is written as sequential code runs relatively quickly but may not translate well into hardware. The same goes for C: it runs very quickly and is well suited for software, but not for specifying hardware.

Dataflow and finite-state models of computation have been shown to be reasonably retargettable. Hierarchical FSMs such as Statecharts can be used effectively to design hardware or software. It has also been shown that a single dataflow specification can be partitioned for combined hardware and software implementation.'[6]

[Guus: to be done. Explain that not all tools support all phases of (co-) design process. I.e. some simulation only; others formal verification only.]

What phases of the development process are supported in the approach?

## 5.6 Conclusion

In this chapter various requirements for modern system-level design methods have been discussed. The following points should be covered by Co-Design approaches:

- 1. How is integration of various MoCs dealt with

- 2. What is the origin of the IDR of the approach

- 3. Is there a possibility of design-space exploration in the approach?

- 4. Does the approach allow IP re-use

- 5. What type of target-architectures are supported

- 6. The abstraction level of the approach

- 7. Is there a 'gap' in the development process; what phases of the process are supported

- 8. Is (automatic) partitioning supported (if the approach allows synthesis at all)

These aspects will be taking into account in the next Chapter, where a number of Co-Design methodologies will be analyzed.

## Chapter 6

# Co-Design methodologies

In this Chapter we'll see a few of the most famous modelling methods and a few that have been selecting because they are special. [Yes, this should be a different sentence].

## 6.1 Ptolemy II

The Ptolemy project studies heterogeneous modelling, simulation and design of concurrent systems, where the focus is on embedded systems.[11].

The primary investigator of the Ptolemy project is Edward A. Lee. In 1991 he presented a paper that described the Ptolemy system[3]. This system has been in use for many years, and it's now succeeded by a new version, Ptolemy II.

The Ptolemy II software environment provides support for hierarchically combining a large variety of models of computation and allows hierarchical nesting of models[13]. It combines the wish for a homogeneous and thus predictable model with the desire to mix partial models of different kinds in a common heterogeneous model by hierarchically nesting sub-models of potentially different kinds.

A very good description of how this hierarchical mixed approach works in practice can be found in [28].

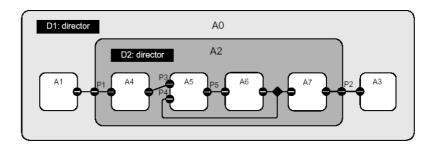

Ptolemy II is a component-based design methodology. The components in the model are called actors. A model is a hierarchial composition of actors. The atomic actors, such as A1, only appear at eh bottom of the hierarchy. Actors that contain other actors, such as A2, are composite. A composite actor can be contained by another composite actor.

Atomic actors contain basic computation, from as simple as an AND gate to more complex as an FFT. Through composition, actors that perform even more complex functions can be built. Actors have ports, which are their communication interfaces. For example in Figure 6.1, A5 receives data from input ports P3 and P4, performs its computation, and sends the result to output port P5. A port can be both an input and an output. Communication channels among actors are established by connecting ports.

The possibility to have various MoC's can be found in the *director*. A director controls the execution order of the actors in a composite, and mediates their

Figure 6.1: Example of a hierarchical specification of a systems using two (possibly different) Models of Computation. The directors controls the flow of control and data in such a MoC.

communication. In figure 1, D1 may choose to execute A1, A2 and A3 sequentially. Whenever A2 is executed, D2 takes over and executes A4-A7 accordingly. A director uses receivers to mediate actor communication. As shown in figure 2, one receiver is created for each communication channel; it is situated at the input ports, although this makes little difference. When the produces actors sends a piece of data (a token) to the output port, the receiver decides how the transaction is completed. Within a composite actor, the actors under the immediate control of a director interact homogeneously.

Ptolemy II is a successor to Ptolemy Classic. It is written in Java, while the original version was made in C++.

The focus in Ptolemy is on simulation. However, Ptolemy is often used in combination with other tools, such as Polis (see Chapter 6.4)[30], to provide co-simulation functionalities. It is possible to use Ptolemy to generate software for specific processors (DSPs) too[37].

Ptolemy does not explicitly support the Y-chart approach [49]. However, Ptolemy is a very extensible system. There is an extension of the Ptolemy kernel in the direction of a Y-chart like tool for evaluation of architecture trade-offs, see [36].

## 6.2 COSYMA

An older design method is COSYMA, "CoSynthesis for Embedded Architectures". It was developed at the IDA, Germany. It covers the entire design flow from specification to synthesis. The target architecture consists of a standard RISC processor, a fast RAM for program and data with single clock cycle access time and an automatically generated application specific co-processors. Communication between processors and co-processor takes place through shared memory. The goal of Cosyma is basically speeding up existing programs by replacing parts in hardware[35].

The system is designed in  $C^x$ . This is a C-extension with support for parallel processes and timing constraints. The  $C^x$  specification is then converted into an Extended Syntax Graph (ESG), the IDR. This is similar to a CDFG. The

6.3. FORSYDE 31

ESG describes a sequence of declarations, definitions and statements and is overlayed with the Data Flow Graph (DFG) containing information about data dependencies. This shows the software-background of the tool, it is something like an extended compiler.

"The chief advantage of this approach is the ability to utilize advanced software structures that result in enlarging the complexity of system designs. However, selective hardware extraction based on potential speedups makes this scheme relatively limited in exploiting potential use of hardware components. Further, the assumption that hardware and software components execute in an interleaved manner (and not concurrently) results in a system that under-utilizes its resources" [16].

Research using COSYMA has been discontinued in 1999.

## 6.3 ForSyDe

For SyDe is a model based on the synchronous-assumption (see Chapter 4.3.10). It has been developed by Sander and Jantsch [38, 39].

In their model events are totally-ordered by their tags. Every signal has the same set of tags. Events with the same tag are processed synchronously. There is a special value  $\perp$  ("bottom") to indicate the absence of an event. These are necessary to establish a total ordering among events. A system is modelled by means of concurrent processes, which are Haskell functions or 'skeletons'.

Fundamental to the approach is the transformation process. The specification of the system is done in Haskell, and an iterative process of rewriting the specifications goes on until the requirements are met. ForSyDe does not allow for architectures do be described in the method, as such it does not support design space exploration directly.

Lu[29] shows how to transform a system specification described in ForSyDe into its hardware and software counterparts. He does not provide a mixed implementation of HW and SW. [Guus: why not per module possible to make this decision?]

The hardware version of the Digital Equalizer that Lu makes is described using behavioral VHDL. The process are described using skeletons and these are then synthesized to VHDL code. The process described is manual. The Haskell code turns into behavioral VHDL quite easily. To generate (naturally sequential) C code an analysis phase is done to create a PASS.

IP reuse has not been specifically addressed.

## 6.4 Polis

The Polis research project started in 1988 by the UC Berkeley. It is a design environment for control-dominated embedded systems. It supports designers in the partitioning of a design and in the selection of a micro-controller and peripherals.

The system specification language is Esterel, but a graphical specification can also be given.

The generated software part consists of:

1. the application that has been modelled in CFSMs

- 2. a generated application-specific operating system for the selected processor

- 3. the I/O drivers

Hardware is synthesized as well. The Polis environment provides an interface for verification and simulation tools as well as an simulator. Automatic partitioning is not supported in Polis.

A fundamental limitation of the Polis system is the MoC used, the Codesign Finite State Machine (CFSM). A CFSM is an extended finite state machine that communicates with other CFSMs asynchronously with unbounded delay and by means of events. The communication model between CFSMs is not efficient in representing systems with intensive data processing, since CFSMs communicate over channels with one-place buffers and have non-blocking write communication semantics. Therefore, a buffer is overwritten every time the sender emits an event before the receiver has consumed the previous event. This can be avoided either by means of scheduling constraints or with a blocking write protocol: however, both mechanisms often result in a loss of performance. This means that POLIS is mainly useful for control-dominated embedded systems. Although the POLIS method allows performance-estimation for the simple controller that is generated, estimation techniques for more complex processor models are lacking [49].

The Polis project has led to a set of commercial tools. For example, the Candence Virtual Component Co-Design toolkit (VCC) has been built op top of Polis. VCC allows better IP reuse than Polis, and follows the Y-chart approach[49]. Because the CSFM is not biased towards either hardware or software, it allows for a very late decision of what part to implement is software and what in hardware. This is also a great help for design space exploration: the options stay open.

## 6.5 SpecC